JPE 15-2-7

http://dx.doi.org/10.6113/JPE.2015.15.2.356 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Single-Phase Bridgeless Zeta PFC Converter with Reduced Conduction Losses

Shakil Ahamed Khan<sup>†</sup>, Nasrudin Abd. Rahim<sup>\*</sup>, Ab Halim Abu Bakar<sup>\*</sup>, and Tan Chia Kwang<sup>\*</sup>

<sup>†\*</sup>UM Power Energy Dedicated Advanced Centre (UMPEDAC), University of Malaya, Kuala Lumpur, Malaysia

#### Abstract

This paper presents a new single phase front-end ac-dc bridgeless power factor correction (PFC) rectifier topology. The proposed converter achieves a high efficiency over a wide range of input and output voltages, a high power factor, low line current harmonics and both step up and step down voltage conversions. This topology is based on a non-inverting buck-boost (Zeta) converter. In this approach, the input diode bridge is removed and a maximum of one diode conducts in a complete switching period. This reduces the conduction losses and the thermal stresses on the switches when compare to existing PFC topologies. Inherent power factor correction is achieved by operating the converter in the discontinuous conduction mode (DCM) which leads to a simplified control circuit. The characteristics of the proposed design, principles of operation, steady state operation analysis, and control structure are described in this paper. An experimental prototype has been built to demonstrate the feasibility of the new converter. Simulation and experimental results are provided to verify the improved power quality at the AC mains and the lower conduction losses of the converter.

Key words: AC-DC converter, Bridgeless rectifier, Conduction losses, Power factor correction, Zeta converter

#### I. Introduction

In recent years, single phase ac-dc PFC converters have received much attention due to the dramatic growth in the use of electronic equipment and these ac-dc converters introduce harmonic currents. These harmonic currents cause a lower power factor at the ac mains, voltage distortion and noise [1]-[3]. To comply with harmonic standards and to increase transmission efficiency in power systems, PFC techniques are necessary in ac-dc power converters [4], [5]. In addition, electronic equipment benefits from power converters with high efficiency over a wide range of input and output voltages [6]. However, conventional ac-dc converter designs cannot deliver high efficiency over a wide operation range in both step up and step down voltage conversions and it is difficult to design the control system. Therefore, a new topology design that improves efficiency and reduces the complexity of the control is desirable. In this paper, a novel bridgeless PFC rectifier topology is proposed to achieve these objectives.

The most common PFC converter architecture in the market consists of a front-end diode bridge rectifier circuit where the bridge rectifier is followed by a boost dc-dc converter. The boost converter is popular in PFC converter architecture due to its simple circuit, simple control scheme and low input current harmonics [7]-[13]. However, this architecture is not suitable for high power applications because of the high conduction losses caused by the input diode bridge. In addition, three semiconductors exist in the current flowing path in a complete switching period. Furthermore, one significant drawback of the boost converter which is used in the architecture is that the output voltage of the boost converter is always higher than the input voltage. Besides, the converter does not have the capability to protect against short circuits or load overcurrent [14].

Unlike boost converter, Cuk and SEPIC converters can be operated as a voltage step up or step down converter. However, these converters are not able to protect against the startup inrush current condition. Therefore, an additional circuit is necessary to protect against inrush current [4], [14].

To avoid the rectifier input bridge, a number of bridgeless PFC converter topologies have been proposed by numerous

Manuscript received Oct. 14, 2014; accepted Jan. 03, 2015

Recommended for publication by Associate Editor Joung-Hu Park.

†Corresponding Author: shakil\_pilabs@yahoo.com

Tel: +603-22463397, Fax: +603-22463257, University of Malaya

\*UM Power Energy Dedicated Advanced Centre (UMPEDAC), University of Malaya, Malaysia

authors [12], [15]-[26]. Most of the proposed bridgeless PFC converters utilize a boost topology because of its high efficiency, improved power factor, and simple control scheme. When compared to the boost ac–dc PFC topology, the bridgeless PFC converter solves the heat problem generated by the input bridge rectifier. In addition, current flows through two semiconductor devices during each switching cycle which significantly reduces the total conduction losses. However, the rectifier has the same drawbacks as the boost converter. Furthermore, a complex circuit is needed to sense the current in the MOSFET and diode paths separately, and this topology has the problem of a high startup inrush current [27].

To overcome these constraints, a new single phase bridgeless PFC topology based on Zeta converter is proposed in this paper. The conduction losses are reduced in the proposed converter topology when compare to the conventional PFC converter due to the reduced number of semiconductors in the flowing current path. In addition, a wider operation range (up-and-down voltage conversion) can be achieved. The proposed converter is operated in DCM. Therefore, current loop is not required to shape the input current. As a result, the control circuit is simplified. In addition, the main switch is turned on and the output diode is turned off under zero current switching condition due to the DCM operation. Furthermore, this converter is capable of protecting itself against overload and inrush current. The proposed rectifier topology utilizes four inductors, which are described as a drawback of the topology. However, implementation of the coupled inductor technique can be used to reduce the magnetic components count.

The organization of this paper is as follows: Section 2 presents the new proposed topology design, the principle of operation and analysis. The converter design procedure and an example are explained in detail in Section 3, followed by an efficiency comparison with conventional converter techniques. Section 4 presents simulation results. Section 5 provides experimental validation and analysis of the proposed topology.

# II. OPERATION AND ANALYSIS

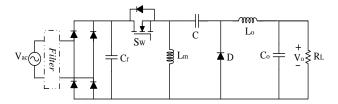

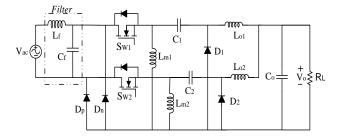

The power stages of a conventional Zeta PFC rectifier and the proposed bridgeless Zeta PFC rectifier are shown in Fig. 1 and Fig. 2, respectively. The new topology is derived by connecting two ZETAs. The proposed converter acts as a conventional Zeta converter during the positive input source voltage and as an inverting Zeta converter during the negative input source voltage with the same DC voltage gain for either polarity of the input source voltage. The proposed topology utilizes two control switches. However, these switches (Sw $_1$  and Sw $_2$ ) can be driven with the same PWM signal, which reduces the complexity of the rectifier control circuit.

Fig. 1. Conventional Zeta PFC rectifier [28].

Fig. 2. Proposed bridgeless Zeta PFC.

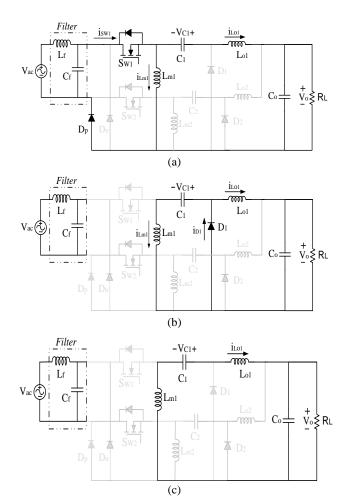

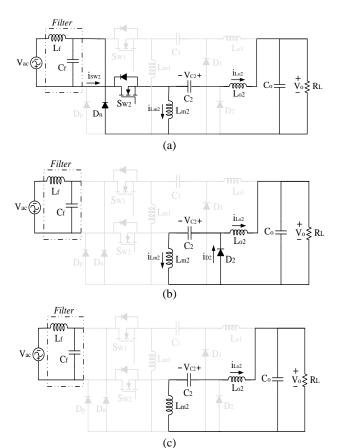

Fig. 3 and Fig. 4 show the operational circuits of the proposed topology during the positive and negative half cycles of the input voltage, respectively. Referring to Fig. 3 and Fig. 4, one switch and one diode conduct in mode I and only one diode conducts in mode II. Therefore the conduction losses are reduced when compare to the conventional PFC converter. The converter operation is symmetrical in each of the half cycles of the input line voltage. Therefore, it is sufficient to explain the rectifier operation during one complete switching period  $(T_s)$  in a positive half period of the input voltage. It is assumed that the inductors in the converter are working in DCM. The operation of the Zeta converter in DCM has several advantages over continuous conduction mode (CCM) operation. These advantages are that the control circuit of the converter is simplified and includes soft turn on of the switch, reduced reverse recovery losses of the diode and inherent power factor correction. To simplify the analysis of the converter, it is assumed that the circuit is operating under the steady state condition and that all of the circuit elements of the converter are considered ideal. Furthermore, the output capacitance is considered to be large enough to make its voltage constant. In addition, the input voltage is assumed to be constant during a switching period.

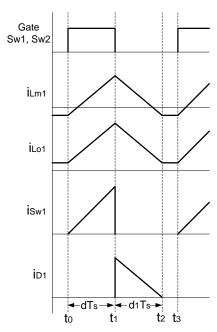

According to the above assumptions, the converter operation can be classified into three stages in a switching cycle. Theoretical waveforms of the converter in DCM during a complete switching period (Ts) are shown in Fig. 5.

First stage  $(t_0, t_1)$ : When the switch is in the on state, the input source supplies energy to the inductors  $L_{ml}$  and  $L_{ol}$ , and the current through the inductors increase linearly. The voltages across the capacitors  $C_1$  and  $C_o$  are considered to be constant and equal to  $V_o$ . In this stage, the diode  $D_1$  is blocked by a reverse voltage  $V_{Df}$  that is given by:

$$V_{Df} = -(V_{in} + V_o) \tag{1}$$

Fig. 3. Proposed converter operation in different modes (a-c) for positive half cycle of line voltage. (a) Mode II. (b) Mode III. (c) Mode III.

Second stage  $(t_1, t_2)$ : When the switch is turned off, the diode  $D_1$  starts to conduct, and the inductors currents  $iL_{ml}$  and  $iL_{ol}$  decrease linearly. In this stage, no energy circulates in the main line. As a result, the harmonic distortion is eliminated in the input line current. The voltage across the switch is given by:

$$V_{Sw} = V_{in} + V_{o} \tag{2}$$

Third stage  $(t_2, t_3)$ : In this stage, when the currents through the inductors  $L_{ml}$  and  $L_{ol}$  become equal, the diode  $D_1$  turns off. The voltages applied to the inductors  $L_{ml}$  and  $L_{ol}$  are zero and the current is constant until the switch is turned on.

The input voltage  $V_{in}$  of the converter is given by the following equation:

$$V_{in} = V_m \cdot \sin(\omega t) \tag{3}$$

Referring to the first stage, the following input and output inductors current equations can be obtained.

$$i_{L_{m_1}}(t) = \frac{V_m}{L_{m_1}} t.\sin(\omega t) + iL_{m_{1,\min}}$$

(4)

Fig. 4. Proposed converter operation in different modes (a-c) for negative half cycle of line voltage. (a) Mode I. (b) Mode II. (c) Mode III.

$$i_{Lo_1}(t) = \frac{V_m}{L_{o1}} t. \sin(\omega t) + iL_{o1,\min}$$

(5)

Where  $iL_{m1,\,\mathrm{min}}$  and  $iL_{o1,\,\mathrm{min}}$  are the minimum inductor currents through the inductors  $L_{m1}$  and  $L_{o1}$ , respectively. The switch current is given by the sum of the currents through the inductor  $L_{m1}$  and  $L_{o1}$ , resulting in:

$$i_{sw1}(t) = i_{Lm1}(t) + i_{Lo1}(t)$$

(6)

$$i_{sw1}(t) = \frac{V_m}{L_{oo}} t.\sin(\omega t) + iL_{m1, \min} + iL_{o1, \min}$$

(7)

Where:

$$\frac{1}{L_{eq}} = \frac{1}{L_{m1}} + \frac{1}{L_{o1}} \tag{8}$$

The currents  $iL_{m1, \min}$  and  $iL_{o1, \min}$  are equal and opposite. Therefore, the switch current can be expressed as follows:

$$i_{Sw1}(t) = \frac{V_m}{L_{eq}} .t. \sin(\omega t)$$

(9)

Fig. 5. Theoretical waveforms of the converter in DCM.

From Eq. (9), it can be concluded that the main switch Sw<sub>1</sub> turns on under the zero current switching condition.

In the second stage, the current through the inductors decrease linearly and the inductors current equations are given as follows:

$$iL_{m1}(t) = -\frac{V_0}{L_{m1}}.t + \frac{V_m}{L_{m1}}.\sin(\omega t).dT_S + iL_{m1,\min}$$

(10)

$$i_{Lo_1}(t) = -\frac{V_0}{L_{o_1}} t + \frac{V_m}{L_{o_1}} \cdot \sin(\omega t) \cdot dT_S + iL_{o_1, \min}$$

(11)

In the third stage, the diode current is zero. Referring to Fig. 3(b) and Fig. 3(c), the input current does not circulate. The input current in mode I is given by:

$$i_{in}(t) = i_{I,m1}(t) + i_{I,o1}(t)$$

(12)

Since, the currents  $iL_{m1,\, \rm min}$  and  $iL_{o1, \rm min}$  are equal and opposite in polarity, the input current can be simplified as follows:

$$i_{in}(t) = \frac{V_m}{L_{eq}}.t.\sin(\omega t)$$

(13)

The converter has an input filter to eliminate the harmonics. Therefore:

$$i_{in}(t) = \frac{V_m.D}{L_{oo.}f_s}.\sin(\omega t)$$

(14)

Where, D = Duty cycle and fs = switching frequency. From Eq. (14), it can be concluded that the low order harmonics do not exist in the converter [11].

## III. DESIGN PROCEDURE AND EXAMPLE

This topology is derived by connecting two ZETAs. Therefore, the design procedure is similar to the conventional Zeta converter. In this section, an example of the proposed converter with the following specifications is explained.

## A. Input Data

Output power:  $P_{out} = 150 \text{ W}$ Output voltage:  $V_o = 150 \text{ V}$

Switching frequency:  $f_s = 30 \text{ kHz}$

Line frequency:  $f_L = 50$ Hz;

Output voltage ripple:  $\Delta vo = \pm 2\%$  (max) of Vo

Input voltage:

$$V_{in} = V_m \sin(2\pi 50t) = 311 \sin(2\pi 50t)$$

Where,  $V_m$  is the peak input voltage.

The input current can be obtained from the following equation:

$$I_{in} = I_1 \sin(\omega t) = \frac{2P_{out}}{\eta V_m} \sin(\omega t)$$

(15)

If the efficiency is 90%, the input current can be expressed as:

$$I_{in} = 1.07 \sin(2\pi 50t) \tag{16}$$

The equivalent load resistance is:

$$R_{eq} = \frac{V_o^2}{P_{out}} = 150\Omega \tag{17}$$

The output current  $I_o$  is calculated as follows:

$$I_o = \frac{P_{out}}{V_o} = 1A \tag{18}$$

#### B. Ensuring DCM Operation

The critical value of the inductance to operate at the boundary of the CCM and DCM is given as follows [14]:

$$L_{c} = \frac{\alpha N_{m} \cdot D_{c}^{2}}{4.I \cdot f} = 584 \,\mu\text{H} \tag{19}$$

Where:

$$\alpha = \frac{V_m}{V_c} \tag{20}$$

And:

$$D_C = \frac{1}{1+\alpha} \tag{21}$$

Where  $D_c$  is the critical duty cycle.

To ensure the DCM operation, the inductors  $L_{ml}$  and  $L_{m2}$  are selected as 500 $\mu$ H and the output inductances  $L_{ol}$  and  $L_{o2}$  are selected as 500 $\mu$ H [14].

The DC link capacitor is calculated as follows [29]:

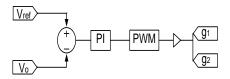

Fig. 6. Controller block diagram.

$$C_o = \frac{I_o}{2\omega\Delta V_o} = 796uF \tag{22}$$

Hence, the value of the DC link capacitor is selected as  $990\mu F$ .

# C. Maximum Ratings of the Switching Devices

The voltage stress of the main switch in the circuit is equal to the sum of the input voltage and the output voltage. Therefore, the maximum voltage across the switch is:

$$V_{SW \text{ max}} = V_m + V_o = 461 \text{ V}$$

(23)

The peak voltage across the diode is:

$$V_{D,peak} = V_m + V_o = 461 \text{ V}$$

(24)

#### D. Control Circuit

The control of the Zeta converter in DCM is relatively simple. Due to the DCM operation, the converter only requires sensing of the output voltage, and current feedback is not required to shape the input current. Thus, the input current sensor can be eliminated. A simplified control block diagram of the converter is shown in Fig. 6.

The proposed converter is controlled using the voltage follower approach and a Pulse Width Modulation (PWM) signal is generated to maintain a desired DC output voltage. The discrete PI control scheme is used for the digital control of the converter. The error between the reference DC link voltage ( $V_{\rm ref}$ ) and the sensed DC link voltage ( $V_{\rm o}$ ) is fed to the PI voltage controller. The function of the discrete PI controller is to generate the control output  $V_{\rm C}$  based on the error voltage  $V_{\rm e}$ .

Where:

$$V_e = V_{ref} - V_o \tag{25}$$

The control output equation of a discrete PI controller at the  $k^{th}$  instant can be expressed as follows:

$$V_C(K) = V_C(K-1) + K_P\{V_e(K) - V_e(K-1)\} + K_i V_e(K)$$

(26) Where:

$K_P$  is the proportional gain, and  $K_i$  is the integral gain of the voltage controller.

The control output  $(V_C)$ , after limiting, is considered to be a modulating signal for the PWM controller to generate the appropriate duty ratio of the switches  $S_{W1}$  and  $S_{W2}$ .

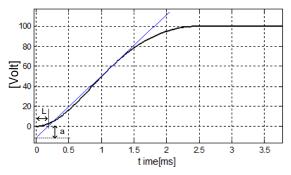

The Ziegler and Nichols suggested rule is used for tuning

Fig. 7. Step response for the tuning of PI controllers according to Ziegler and Nichols Method.

TABLE I

TUNING OF PID CONTROLLER PARAMETERS

ACCORDING TO ZIEGLER AND NICHOLS METHOD [31]

| Controller | $K_p$ | Ti | $T_d$ |

|------------|-------|----|-------|

| P          | 1/a   |    |       |

| PI         | 0.9/a | 3L |       |

| PID        | 1.2/a | 2L | L/2   |

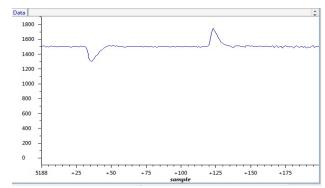

the PI controller ( $K_p$  and  $K_i$ ). This method avoids the need for a model of the complex converter to be controlled, and solely relies on the step response of the converter. The values of the controller are determined based on the transient response characteristics of the converter. The step response curve of the converter is generated from a simulation. The Ziegler and Nichols method applies if the response to a step input exhibits an S-shaped curve [30]. The simulated curve of the converter is also an S-shaped curve, as shown in fig 7.

The parameter for setting the PI controller according to the Ziegler and Nichols method is carried out in four steps as follows [31].

- 1) Obtain the plant step response, as shown in Fig. 7.

- 2) Draw the steepest straight-line tangent to this response.

- 3) Obtain the values of "a" and "L", from Fig. 7.

- 4) Set the parameters according to Table I

According to the Ziegler and Nichols method, the value of  $K_p$  is 0.075, and the value of  $K_i$  is 0.27. The control system of the converter is implemented using a DSP microcontroller (TMS320F28335).

## E. Efficiency Improvement

Based on the circuit operation, the efficiency improvement of the proposed rectifier is verified by calculating the conduction losses of the reduced input bridge diodes during each switching cycle. The power dissipation of each bridge diode due to the conduction loss can be calculated by using the following equation:

$$P_{D,avg} = \frac{1}{T} \int_0^T V_D J_D dt$$

(27)

When the gate signals are turned on, one diode of the

Fig. 8. Simulation waveforms of input voltage and input current.

proposed circuit is reduced in the input current flowing path when compare to the conventional Zeta PFC rectifier circuit. Therefore, the conduction loss of one diode can be calculated as follows:

$$P_{D,avg(on)} = \frac{1}{T} \int_{0}^{T} V_{D} I_{D} . D dt$$

$$= \frac{1}{\pi} \int_{0}^{\pi} 1 * 1.07 * 0.25 \sin(\omega) d\omega$$

(28)

$$P_{D,avg(on)} = 0.17 \,\text{W}$$

(29)

When the gate signals are turned off, the input bridge is omitted from the converter. Therefore, the conduction losses of two diodes can be calculated as follows:

$$\begin{split} P_{D,avg(off)} &= \frac{1}{T} \int_{0}^{T} 2.V_{D}.I_{D}.(1-D)dt & (30) \\ &= \frac{1}{\pi} \int_{0}^{\pi} 2*1*1.07*0.75 \sin(\omega)d\omega \\ &P_{D,avg(off)} = 1.02 \, \text{W} & (31) \end{split}$$

Therefore, the efficiency improvement can be calculated by using the following equation:

$$\eta_{impv} = \frac{P_{D.avg(on)} + P_{D.avg(off)}}{150} = 0.8 \%$$

(32)

# IV. SIMULATION RESULTS

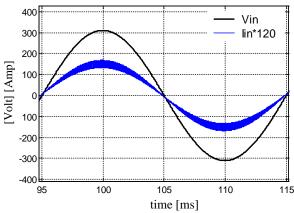

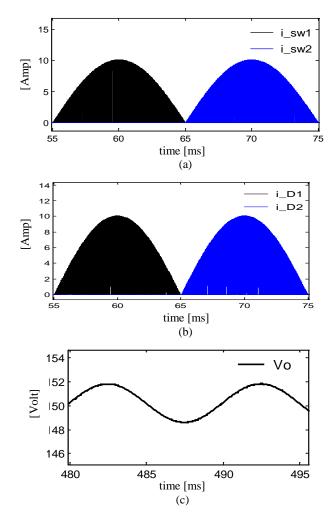

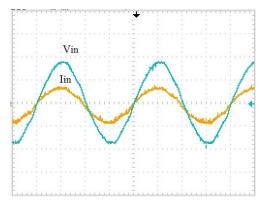

The proposed bridgeless Zeta PFC rectifier is simulated with the following specifications:  $v_{in} = 311 \sin(\omega t)$ ,  $f_L = 50$ Hz,  $f_s = 30$ kHz,  $L_{ml} = L_{m2} = 500\mu$ H,  $L_{ol} = L_{o2} = 500\mu$ H,  $C_1 = C_2 = 1\mu$ F,  $C_o = 990\mu$ F, and  $R_L = 150\Omega$ . Fig. 8 shows the input current and input voltage of the converter under a full load to demonstrate the power quality. It can be observed that the source voltage and source current are in phase and sinusoidal with 4.18% THD of the input current. It can also be seen that the power factor is around 0.994. Since, the converter is operated in

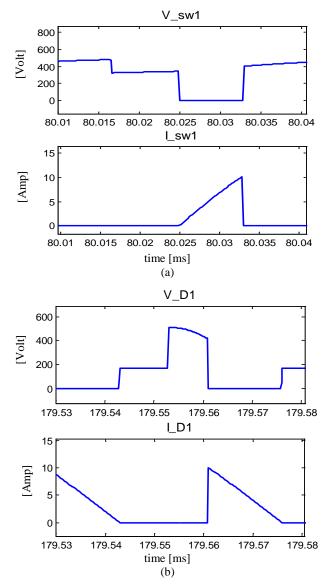

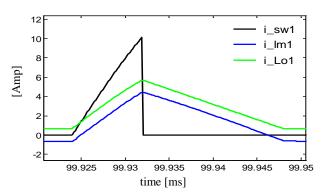

Fig. 9. Simulated waveforms of MOSFET and diode in DCM.

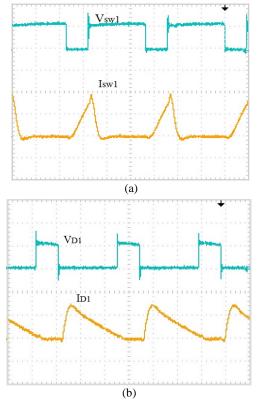

DCM, the main switch is turned on under the zero current switching condition, and the output diode is turned off under the zero current switching condition, as shown in Fig. 9 (a) and Fig. 9 (b), respectively. Therefore, the reverse recovery problem of the diode is resolved by employing the DCM operation of the Zeta converter. The simulated waveforms of the input and output inductor current and the switch current are shown in Fig. 10. Fig. 11 (a) and Fig. 11 (b) show the current of the main switches and output diodes during the positive and negative half cycles of the input voltage, respectively. The peak to peak output voltage ripple is shown in Fig. 11 (c).

# V. EXPERIMENTAL RESULTS

This section presents experimental results of the proposed bridgeless Zeta PFC converter and comparisons with the

Fig. 10. Simulated waveforms for the converter in DCM.

Fig. 11. Simulated waveforms. (a) Switch current. (b) Diode current. (c) DC output voltage.

conventional Zeta PFC converter. The proposed converter operates at 30kHz and utilizes IPP60R099C6 switches with  $R_{\rm DS(on),max}=0.099~\Omega$  and 20ETF06PBF diodes. The prototype parameters of the proposed converter are listed in Table II, and the conventional Zeta PFC converter specifications are as follows:  $L_m=1mH,~L_o=1mH,~C=2\mu F,$  and  $C_o=990\mu F.$  Fig. 12 shows experimental results of the input voltage and input current. It can be observed that the

TABLE II

EXPERIMENTAL CONVERTER PARAMETERS

| Input voltage v <sub>ac</sub>                     | 120 V <sub>rms</sub>            |  |  |

|---------------------------------------------------|---------------------------------|--|--|

| Output voltage V <sub>o</sub>                     | $60  \mathrm{V_{dc}}$           |  |  |

| Output power Pout                                 | 40 W                            |  |  |

| Input inductor Lm <sub>1</sub> =Lm <sub>2</sub>   | 500 μΗ                          |  |  |

| Output inductor L <sub>o1</sub> =L <sub>o2</sub>  | 500 μΗ                          |  |  |

| Coupling capacitor C <sub>1</sub> =C <sub>2</sub> | 1 μF                            |  |  |

| Filter capacitor C <sub>o</sub>                   | 990 μF                          |  |  |

| Switching frequency f <sub>s</sub>                | 30 kHz                          |  |  |

| Diodes $D_1,D_2,D_n,D_p$                          | 20ETF06PBF                      |  |  |

| MOSFET Sw <sub>1</sub> ,Sw <sub>2</sub>           | IPP60R099C6 With                |  |  |

|                                                   | $R_{DS(on),max} = 0.099 \Omega$ |  |  |

Fig. 12. Line voltage and input line current [V: 100V/div, I: 1 A/div, t: 5 ms/div].

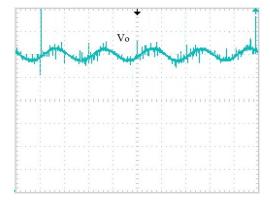

Fig. 13. Output voltage ripple at 60V dc [V: 5V/div, t: 10 ms/div].

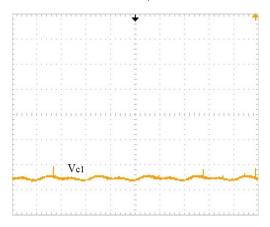

input line current is a perfect replica of the input line voltage and that the measured power factor is near unity. The peak to peak output voltage ripple is less than 4 at 60V of output voltage and 40W of output power, as shown in Fig. 13. Fig. 14 (a) and Fig. 14 (b) illustrate the switching waveforms of the MOSFET and diode, respectively. It can be observed that the MOSFET turns on and the diode turns off under the zero current condition due to the DCM operation of the converter. The voltage of the capacitor C<sub>1</sub> is shown in Fig.15. Fig.16 shows the behavior of the output voltage of the PI controller when the input voltage changes. A comparative analysis of the number of diode conducts during each switching period in

Fig. 14. Voltage and current waveform of (a) switch  $Sw_1$  [V: 200V/div, I: 2A/div, t:10  $\mu s/div$ ] (b) diode  $D_1$  in a switching period [V: 200V/div, I: 2A/div, t:10  $\mu s/div$ ].

Fig. 15. Voltage waveform of capacitor  $C_1$  [V: 50 V/div, t: 5ms/div].

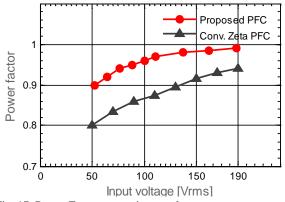

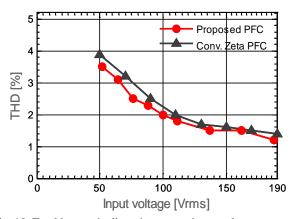

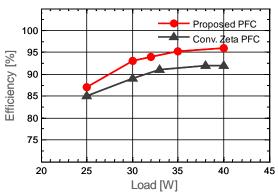

DCM of the proposed converter with the existing bridgeless PFC topologies and the conventional Zeta PFC is shown in Table III. The measured power factor curve of the proposed converter is provided in Fig.17, and it is compared with the conventional Zeta PFC converter. The power factor of the proposed converter is close to 0.99 at 190 Vrms of input voltage. The input current THD of the conventional Zeta and the proposed PFC converter curve is shown in Fig. 18. The measured input current THD of the proposed converter was 1.2% at 190  $\rm V_{rms}$  of input voltage. Fig.19 shows an efficiency comparison between the proposed converter and the

Fig. 16. Behavior of the output voltage of the PI controller, in experiment, due to input voltage variations.

TABLE III

COMPARATIVE ANALYSIS OF PROPOSED CONVERTER

WITH EXISTING PFC TOPOLOGIES IN DCM

| Configuration | No. of diode conducts during each switching stage in DCM |         |         |  |

|---------------|----------------------------------------------------------|---------|---------|--|

| <i>g.</i>     | Stage 1                                                  | Stage 2 | Stage 3 |  |

| BL-Cuk [32]   | 2                                                        | 3       | 2       |  |

| BL-SEPIC[5]   | 2                                                        | 3       | 2       |  |

| Con.Zeta [28] | 2                                                        | 3       | 2       |  |

| Proposed      | 1                                                        | 1       | 0       |  |

Fig. 17. Power Factor versus input voltage curve.

Fig. 18. Total harmonic distortion versus input voltage curve.

Fig. 19. Measured efficiency curve at Vin = 120 Vrms and Vo = 60 V.

conventional Zeta PFC converter. The proposed converter achieves a 96% peak efficiency at 40W of output power, 120  $V_{rms}$  of input voltage and 60V of output voltage.

#### VI. CONCLUSIONS

In this paper, a new bridgeless ac-dc converter with a low input current ripple and lower conduction losses has been presented. The proposed topology addresses several of the disadvantages of the conventional Zeta PFC converter through the development of a new bridgeless topology. The front end bridgeless Zeta PFC converter has been operated in discontinuous conduction mode to achieve an inherent power factor correction. Due to the DCM operation, the current control loop is eliminated and the control circuit is simplified. The main features of the converter are that the input diode bridge is eliminated and the efficiency is improved when compare to a conventional PFC rectifier. The merits of the proposed design include a high efficiency, an improved power factor, low line current harmonics, and operation across a wide range of input and output voltages. In addition, theoretical analyses of the proposed scheme and simulation results have been presented. Finally a prototype of the proposed converter has been built to validate its performance.

# ACKNOWLEDGMENT

The authors thank University of Malaya for supporting this work through HIR Grant Campus Network Smart Grid System for Energy Security (Grant no: H-16001-00-D000032).

#### REFERENCES

- [1] N. Altintaş, "A novel single phase soft switched PFC converter," *Journal of Electrical Engineering & Technology*, Vol. 9, No. 5, pp. 1592-1601, Sep. 2014.

- [2] B. Singh and S. Singh, "PFC bridge converter for voltage-controlled adjustable-speed PMBLDCM drive," *Journal of Electrical Engineering & Technology*, Vol. 6, No. 2, pp. 215-225, Mar. 2011.

- [3] R. Kalpana, "Direct single-stage power converter with power factor improvement for switched mode power supply," *Journal of Electrical Engineering & Technology*, Vol. 5, No. 3, pp. 468-476, Sep. 2010.

- [4] E. H. Ismail, "Bridgeless SEPIC rectifier with unity power factor and reduced conduction losses," *IEEE Trans. Ind. Electron.*, Vol. 56, No. 4, pp. 1147-1157, Apr. 2009.

- [5] M. Mahdavi and H. Farzanehfard, "Bridgeless SEPIC PFC rectifier with reduced components and conduction losses," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 9, pp. 4153-4160, Sep. 2011.

- [6] H. Jingying, A. D. Sagneri, J. M. Rivas, H. Yehui, S. M. Davis, and D. J. Perreault, "High frequency resonant SEPIC converter with wide input and output voltage ranges," in *Conf. PESC* 2008, pp. 1397-1406, 2008.

- [7] M. Mahdavi and H. Farzanehfard, "Zero-current-transition bridgeless PFC without extra voltage and current stress," *IEEE Trans. Ind. Electron.*, Vol. 56, No. 7, pp. 2540-2547, Jul. 2009.

- [8] M. Kazerani, P. D. Ziogas, and G. Joos, "A novel active current waveshaping technique for solid-state input power factor conditioners," *IEEE Trans. Ind. Electron.*, Vol. 38, No. 1, pp. 72-78, Feb. 1991.

- [9] A. R. Prasad, P. D. Ziogas, and S. Manias, "An active power factor correction technique for three-phase diode rectifiers," *IEEE Trans. Power Electron.*, Vol. 6, No. 1, pp. 83-92, Jan. 1991.

- [10] S. Bin and L. Zhengyu, "An interleaved totem-pole boost bridgeless rectifier with reduced reverse-recovery problems for power factor correction," *IEEE Trans. Power Electron.*, Vol. 25, No. 6, pp. 1406-1415, Jun. 2010.

- [11] C. Jung-Goo, B. Ju-Won, Y. Dong-Wook, and H.-S. Lee, "Reduced conduction loss zero-voltage-transition power factor correction converter with low cost," *IEEE Trans. Ind. Electron.*, Vol. 45, No.3, pp. 395-400, Jun. 1998.

- [12] T. Hsien-Yi, H. Tsun-Hsiao, and C. Dan, "A family of zero-voltage-transition bridgeless power- factor- correction circuits with a zero-current-switching auxiliary switch," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 5, pp. 1848-1855, May. 2011.

- [13] J. Yungtaek and M. M. Jovanovic, "A bridgeless PFC boost rectifier with optimized magnetic utilization," *IEEE Trans. Power Electron.*, Vol. 24, No. 1, pp. 85-93, Jan. 2009.

- [14] A. Peres, D. C. Martins, and I. Barbi, "ZETA converter applied in power factor correction," in *Conf. PESC 1994*, pp. 1152-1157,1994.

- [15] J. C. Salmon, "Circuit topologies for single-phase voltage-doubler boost rectifiers," in *Conf. APEC 1992*, pp. 549-556, 1992.

- [16] P. N. Enjeti and R. Martinez, "A high performance single phase AC to DC rectifier with input power factor correction," in *Conf. APEC 1993*, pp. 190-195, 1993.

- [17] A. F. de Souza and I. Barbi, "A new ZVS semiresonant high power factor rectifier with reduced conduction losses," *IEEE Trans. Ind. Electron.*, Vol. 46, No. 1, pp. 82-90, Feb. 1999.

- [18] W. Chien-Ming, "A novel zero-Voltage-switching PWM boost rectifier with high power factor and low conduction losses," *IEEE Trans. Ind. Electron.*, Vol. 52, No. 2, pp. 427-435, Apr. 2005.

- [19] G. Moschopoulos and P. K. Jain, "A novel single-phase soft-switched rectifier with unity power factor and minimal component count," *IEEE Trans. Ind. Electron.*, Vol. 51, No. 3, pp. 566-576, Jun. 2004.

- [20] L. Bing, R. Brown, and M. Soldano, "Bridgeless PFC implementation using one cycle control technique," in *Conf. APEC 2005*, pp. 812-817, 2005.

- [21] C. Woo-Young, K. Jung-Min, E.-H. Kim, J.-J. Lee, and K. Bong-Hwan, "Bridgeless boost rectifier with low conduction losses and reduced diode reverse-recovery problems," *IEEE Trans. Ind. Electron.*, Vol. 54, No. 2, pp. 769-780, Apr. 2007.

- [22] L. Huber, J. Yungtaek, and M. M. Jovanovic, "Performance evaluation of bridgeless PFC boost rectifiers," *IEEE Trans. Power Electron.*, Vol. 23, No. 3, pp. 1381-1390, May 2008.

- [23] W. Wenfei, D. D. C. Lu, and G. M. Chu, "Digital control of bridgeless buck PFC converter in discontinuous-input-voltage-mode," in *Conf. IECON 2011*, pp. 1312-1317, 2011.

- [24] M. R. Sahid, A. H. M. Yatim, and T. Taufik, "A new AC-DC converter using bridgeless SEPIC," in *Conf. IECON* 2010, pp. 286-290, 2010.

- [25] A. J. Sabzali, E. H. Ismail, M. A. Al-Saffar, and A. A. Fardoun, "New bridgeless DCM sepic and cuk PFC rectifiers with low conduction and switching losses," *IEEE Trans. Ind. Appl.*, Vol. 47, No. 2, pp. 873-881, Apr. 2011.

- [26] J. P. R. Balestero, F. L. Tofoli, R. C. Fernandes, G. V. Torrico-Bascope, and F. J. M. De Seixas, "Power factor correction boost converter based on the three-state switching cell," *IEEE Trans. Ind. Electron.*, Vol. 59, No. 3, pp. 1565-1577, Mar. 2012.

- [27] F. Musavi, W. Eberle, and W. G. Dunford, "A high-performance single-phase bridgeless interleaved PFC converter for plug-in hybrid electric vehicle battery chargers," *IEEE Trans. Ind. Appl.*, Vol. 47, No. 4, pp. 1833-1843, Aug. 2011.

- [28] Z. Hao, Z. Yuan, and M. Xikui, "Distortion behavior analysis of general pulse-width modulated zeta PFC converter operating in continuous conduction mode," *IEEE Trans. Power Electron.*, Vol. 27, No. 10, pp. 4212-4223, Oct. 2012.

- [29] B. Singh, S. Singh, A. Chandra, and K. Al-Haddad, "Comprehensive study of single-phase AC-DC power factor corrected converters with high-frequency isolation," *IEEE Trans. Ind. Informat.*, Vol. 7, No. 4, pp. 540-556, Nov. 2011.

- [30] K. Ogata, Modern Control Engineering, Prentice Hall, chap. 10, 2001.

- [31] J. C. B. a. S. R. Matos, "Design of PI and PID controllers with transient performance specification," *IEEE Trans. Education*, Vol. 45, No. 4, pp. 364-370, Nov. 2002.

- [32] A. A. Fardoun, E. H. Ismail, A. J. Sabzali, and M. A. Al-Saffar, "New efficient bridgeless cuk rectifiers for PFC applications," *IEEE Trans. Power Electron.*, Vol. 27, No. 7, pp. 3292-3301, Jul. 2012.

Shakil Ahamed Khan received the B.Sc. degree in Electrical & Electronic Engineering from Rajshahi University of Engineering & Technology, Bangladesh. He is currently a Masters student in UM Power Energy Dedicated Advanced Centre (UMPEDAC), University of Malaya. His research interests include smart grid,

modeling and analysis of power electronics circuits and control for power electronics systems.

Nasrudin Abd. Rahim received the B.Sc. (Hons.) and M.Sc. degrees from the University of Strathclyde, Glasgow, U.K., and the Ph.D. Degree from Heriot-Watt University, Edinburgh, U.K., in 1995. He is currently a Professor as well as the Director of UM Power Energy Dedicated Advanced Centre (UMPEDAC). His research interests

include power electronics, real-time control systems, and electrical drives. Prof. Dr. Nasrudin Abd Rahim is also a fellow member for both the Institution of Engineering and Technology (IET), and the Academy of Sciences Malaysia. He is also a Chartered Engineer.

Ab Halim Abu Bakar received the B.Sc. degree in Electrical Engineering from the University of Southampton, United Kingdom in 1976, and the M.Eng. and Ph.D. degrees from the University of Technology, Malaysia in 1996 and 2003. He has 30 years of utility experience in Malaysia before joining academia. Currently he is an Expert

Consultant with the UM Power Dedicated Advanced Centre (UMPEDAC), University of Malaya, Malaysia.

**Tan Chia Kwang** graduated with Ph.D. in Electrical Engineering in 2013 from Universiti Tenaga Nasional, Malaysia. He has served as a researcher in TNB Research Sdn Bhd, the research arm of Malaysian Utility Company (TNB) for more than 2 years. He is currently a Senior Lecturer in UM Power Energy Dedicated Advanced

Centre (UMPEDAC).